# DigDes: Digital Design

#### $Naoki\ Pross-{\tt naoki.pross@ost.ch}$

Spring Semester 2021

#### Abstract

This document is "open source", you can find the LATEX sources at https://github.com/NaoPross/DigDes. All diagrams were made with TikZ. The content is based on the material of Prof. Dr. Zbinden, from the course *Digital Design* at the University of Applied Sciences Eastern Switzerland (OST). If you find typos or errors you can open an PR on Github or mail me at naoki.pross@ost.ch if I'm still around (until spring 2022) or np@Ohm.ch.

#### Contents

| 1 | реv  | velopment model                            | T |

|---|------|--------------------------------------------|---|

| 2 |      | SIC Hardware Description Language (VHDL)   | 1 |

|   | 2.1  | Basic syntax and identifiers               | 1 |

|   | 2.2  | Structure and Libraries                    | 1 |

|   | 2.3  | Entities and Architectures                 | 1 |

|   | 2.4  | Type system                                | 2 |

|   |      | 2.4.1 Electric types                       | 2 |

|   |      | 2.4.2 Arithmetic types                     | 2 |

|   |      | 2.4.3 Array type                           | 2 |

|   |      | 2.4.4 Custom enumeration types             | 2 |

|   |      | 2.4.5 Physical types                       | 2 |

|   |      | 2.4.6 Reisizing vectors                    | 3 |

|   |      | 2.4.7 Type casting and conversion          | 3 |

|   | 2.5  | Declarations                               | 3 |

|   | 2.6  | Concurrent Area                            | 4 |

|   |      | 2.6.1 Signal assignment and simple gates   | 4 |

|   |      | 2.6.2 Aggregates                           | 4 |

|   |      | 2.6.3 Selective and conditional assignment | 4 |

|   |      | 2.6.4 Components                           | 4 |

|   |      | 2.6.5 Processes                            | 4 |

|   | 2.7  | Pitfalls and RTL model                     | 5 |

|   | 2.8  | Generic Parameters                         | 5 |

|   |      | 2.8.1 Generic entity and declaration       | 5 |

|   |      | 2.8.2 Generic mapping (Concurrent Area)    | 5 |

| 3 | Stat | te Machines                                | 6 |

|   | 3.1  | Encoding the state                         | 6 |

|   | 3.2  | Updating the state register (Z)            | 6 |

|   | 3.3  | Updating the state $(G)$                   | 6 |

|   | 3.4  | Updating the output (F)                    | 6 |

|   |      |                                            |   |

| 4 | Tes  | ting                                       | 7 |

|   | 4.1  | Simulator                                  | 7 |

|   | 4.2  | Transport delay                            | 7 |

|   | 4.3  | Generate stimuli                           | 7 |

|   | 4.4  | Assertions                                 | 7 |

| 5 | San  | nples / Templates                          | 7 |

#### License

This work is licensed under a Creative Commons "Attribution-NonCommercial-ShareAlike 4.0 International" license.

## 1 Development model

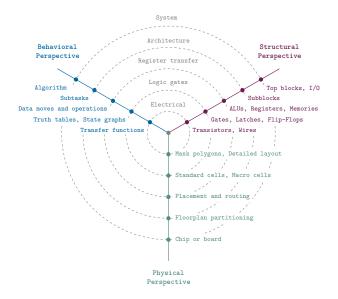

The workflow for the development is show in figure 1. In the Gajski-Kuhn Y-model has 3 axis for the perspectives of the product. It is typical to start from the behavioral axis, by treating the systems as a black-box, and then to jump back and forth between the other axis while gravitating towards the origin (project goal).

Figure 1: Gajski-Kuhn Y-chart.

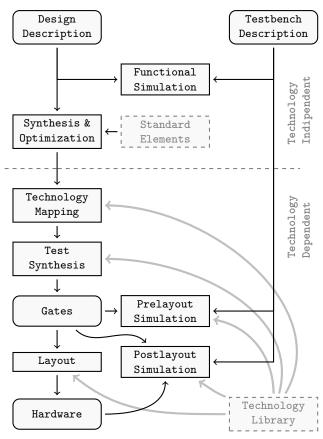

Figure 2 shows a typical flow diagram of how an ASIC device is designed.

## 2 VHSIC Hardware Description Language (VHDL)

#### 2.1 Basic syntax and identifiers

In VHDL an identifier is a case insensitive string composed of A-Z a-z 0-9 \_ that

- is not a keyword,

- does not start with a number or \_,

- does not have two or more \_ in a row.

Expressions are terminated by a semicolon;. Two dashes in a row cause the rest of the line to be interpreted as a comment.

```

1 expression; -- comment

```

#### 2.2 Structure and Libraries

The VHDL code is organized into *libraries* declared with the <code>library</code> keyword. The library of your code is called work, standard features (bit, integer, ...) are found in std, and IEEE standard parts are in ieee. work and std are always implicit and must not be declared.

```

1 library \langle library \ name \rangle;

```

Figure 2: Design flow for an ASIC device.

Once declared a library is composed of packages, which can contain elements (constants, entities, ...). To access the elements the syntax is

```

1 \langle library \rangle. \langle package \rangle. \langle element \rangle;

```

To avoid having to write a long name every time it is possible to import names using

```

1 use \langle library \rangle. \langle element\ or\ all \rangle;

2 use \langle library \rangle. \langle package \rangle. \langle element\ or\ all \rangle;

```

#### 2.3 Entities and Architectures

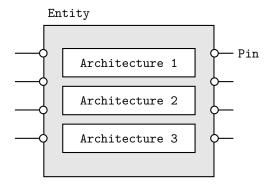

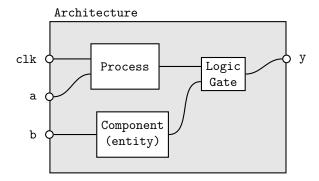

In VHDL the concept of *entity* describes a black box of which only inputs and outputs are known. The internals of an entity are described through an *architecture*. There can be multiple architectures for a single entity.

Entities are declared with port() that may contain a list of pins. Pins have a mode that can be in input (only LHS<sup>1</sup>), out output (only RHS<sup>2</sup>), inout bidirectional or buffer that can stay both on LHS and RHS. The usage of the latter is discourareged in favour of an internal signal.

<sup>&</sup>lt;sup>1</sup>Left hand side

$<sup>^2{\</sup>rm Right}$  hand side

Figure 3: An entity is a black box, that can have multiple architectures.

```

6 );

7 end entity [name];

```

Architectures are normally named after the design model, examples are behavioral, structural.

#### 2.4 Type system

#### 2.4.1 Electric types

VHDL provides some types such as

- boolean true or false,

- bit 0 or 1,

- bit\_vector one dimensional array of bits,

- integer 32-bit binary representation of a value.

From external (standard) libraries other types are available:

- std\_logic advanced logic with 9 states,

- std\_ulogic same as the previous but *unresolved*.

The above are from the <code>ieee.std\_logic\_1164</code> library, and can take the values described in table 1. For the resolved types, i.e. <code>std\_logic</code> types, when a signal is multiply driven the conflict is resolved according to table 2. Unresolved types will give a synthesization error. A good example is a tri-state bus:

```

1 architecture tristate of buscontrol is

2 begin

bus_read: inp <= bus_io;</pre>

5

bus_write: process(enable, oup)

6

begin

bus_io <= (others => 'Z');

7

if enable = '1' then

8

bus_io <= oup;</pre>

9

10

end if;

11

end process:

12 end architecture tristateout;

```

| Value | Meaning        | Usage                   |

|-------|----------------|-------------------------|

| U     | Uninitialized  | In the simulator        |

| X     | Undefined      | Simulator sees a bus    |

|       |                | conflict                |

| 0     | Force to 0     | Low state of outputs    |

| 1     | Force to 1     | High state of outputs   |

| Z     | High Impedance | Three state ports       |

| W     | Weak Unknown   | Simulator sees weak a   |

|       |                | bus conflict            |

| L     | Weak Low       | Open source outputs     |

|       |                | with pull-down resistor |

| H     | Weak High      | Open drain output with  |

|       |                | pull-up resistor        |

| -     | Don't care     | Allow minimization      |

Table 1: Possible values for std\_logic signals.

|   | U | X | 0 | 1 | Z | W | L | Н | - |

|---|---|---|---|---|---|---|---|---|---|

| U | U | U | U | U | U | U | U | U | U |

|   | U | X | X | X | X | X | Х | Х | X |

|   | U | X |   |   |   |   |   | 0 | X |

| 1 | U | X | X | 1 | 1 | 1 | 1 | 1 | X |

| Z | U | Х | 0 | 1 | Z | W | L | Н | Х |

| W | U | Х | 0 | 1 | W | W | W | W | Х |

| L | U | Х | 0 | 1 | L | W | L | W | Х |

| Н | U | Х | 0 | 1 | Н | W | W |   |   |

| _ | U | Х | Х | Х | Х | Х | Х | Х | Х |

|   |   |   |   |   |   |   |   |   |   |

Table 2: Resolution table when a std\_logic signal is multiply driven.

#### 2.4.2 Arithmetic types

For arithmetic operations two more types signed and unsigned (as well as their unresolved equivalents u\_signed and u\_unsigned) can be imported (together with many others for ex. natural) from the library ieee.numeric\_std. Arithmetic types support the operations in table 3.

#### 2.4.3 Array type

Arrays types (fields) of other types can be define with the following.

#### 2.4.4 Custom enumeration types

It is possible to create custom types, usually to create state machines.

```

1 type \langle name \rangle is (\langle identifier \rangle, \langle identifier \rangle, ...);

```

#### 2.4.5 Physical types

For variables that represent physical dimensions it is possible to create values with units with the following:

```

1 type \langle name \rangle is range \langle min \rangle to \langle max \rangle 2 units

```

| Syntax | Operator       | Note                                               |

|--------|----------------|----------------------------------------------------|

| +      | Addition       |                                                    |

| -      | Subtraction    |                                                    |

| abs()  | Absolute value |                                                    |

| *      | Multiplication |                                                    |

| /      | Division       | Typically not available                            |

| **     | Power          | Only powers of 2                                   |

| mod    | Modulo         | Only modulo of $2^k$                               |

| rem    | Remainder      | Only of division by $2^k$                          |

| =      | Equality       |                                                    |

| /=     | Inequality     |                                                    |

| <, >   | Lower, greater |                                                    |

| <=, >= | Lower, greater | Same the assignment                                |

|        | or equal       | operator, however it is always clear from context. |

Table 3: Arithmetic operations from the numeric\_std library.

```

3  \ \langle base unit \rangle;

4     [multiples of base unit];

5  end units;

for example:

1  type CAPACITANCE is range 0 to 1E30

2  units

3     pf;

4     nf = 1000 pf;

5     uf = 1000 nf;

6     mf = 1000 uf;

7  end units;

```

#### 2.4.6 Reisizing vectors

VHDL has a function

that allow to reisze vector types. When resizing a vector of signed type to a higher number of bits the resize function cleverly fills the extra bits 1s or 0s to not mess up the two's complement. Toghether with the resize function an often used feature is the 'length attriubte, that returns the size (in bits) of the identifier.

```

1 y <= resize(a, y'length);</pre>

```

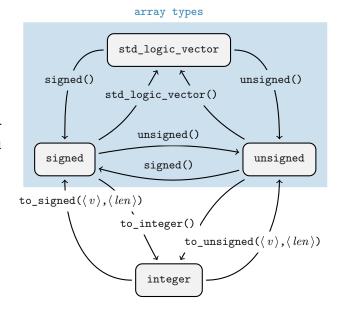

#### 2.4.7 Type casting and conversion

When two signals have the same underlying type it is always possible to perform a *type cast* using the following syntax.

```

1 \langle destination \rangle = \langle type \ name \rangle (\langle source \rangle);

For example:

```

```

1 architecture behavoral of cast_example

2  signal a_int, b_int :

3   std_logic_vector(3 downto 0);

4  signal s_int : unsigned(3 downto 0);

5 begin

```

When the conversion is between signals with a different underlying type it is a (potentially lossy) type conversion. The syntax for a conversion is:

```

1 \langle destination \rangle = to_{\langle type\ name \rangle} (\langle source \rangle);

```

#### 2.5 Declarations

Before a begin – end block, there is usually a list of declarations. A self evident examples are *constants*.

```

1 constant \langle name \rangle : \langle type \rangle := \langle value \rangle;

```

Next, *signals* and *variables*. Signals is are wires, they can only be connected and do not have an initial state. Variables can be assigned like in software, but can cause the synthesization of an unwanted D-Latch.

```

1 signal \langle name \rangle, [name, ...] : \langle type \rangle;

2

3 variable \langle name \rangle, [name], [...] : \langle type \rangle;

4 variable \langle name \rangle : \langle type \rangle := \langle expression \rangle;

```

For the hierarchical designs, when external entities are used, they must be declared as components. The port() expression must match the entity declaration.

```

component (entity name) is

port(

[list of pins]

);

end component;

```

For entities with multiple architectures, it is possible to choose which architecture is used with the following expression.

```

1 for \langle label \ or \ all \rangle: use entity \langle library \rangle.

\hookrightarrow \langle entity \rangle (\langle architecture \rangle);

```

Figure 4: In the concurrent area statements are not interpreted sequentially.

#### 2.6 Concurrent Area

In the architecture between begin and end, the expressions are *not* read sequentially, everything happens at the same time. Statements inside the concurrent area optionally have a label.

```

1 [label]: \( \concurrent \statement \);

```

In the concurrent area signals, components and processes can be used to create a logic.

#### 2.6.1 Signal assignment and simple gates

Signals are assigned using <=.

```

1 [label]: \langle signal \rangle \leftarrow \langle expression \rangle;

```

Simple logic functions such as not, and, or, xor, etc. can be used.

```

1 y <= (a and s) or (b and not(s));</pre>

```

#### 2.6.2 Aggregates

For vector types it is possible to create a value out of multiple signals.

```

1 \langle vector \rangle <= (

2 \langle index \rangle => \langle source or value \rangle,

3 \langle index \rangle => \langle source or value \rangle,

4 [others] => \langle source or value \rangle

5 );

1 -- declaration

2 signal data : bit_vector(6 downto 0);

3 signal a, b : bit;

1 -- concurrent

2 data = (1 => a, 0 => b, others => '0')

```

#### 2.6.3 Selective and conditional assignment

Higher level conditions can be written in two ways.

```

1 -- using when 2 [label]: y <= \langle source \rangle when \langle condition \rangle else 3 \langle source \rangle when \langle condition \rangle else 4 \langle source \rangle when \langle condition \rangle;

```

```

1 -- using with

2 [label]: with \langle signal \rangle select \langle dest \rangle <=

3 \langle source \rangle when \langle value \rangle,

4 \langle source \rangle when \langle value \rangle,

5 \langle source \rangle when others;

```

#### 2.6.4 Components

External components that have been previously declared can be used with the port  $map(\langle assignments \rangle)$  syntax. For example:

```

1 -- declaration

2 component flipflop is

3

port(

4

clk, set, rst : in std_ulogic,

5

Q, Qn

: out std_ulogic

);

6

7 end component flipflop;

9 signal clk_int, a, b : in std_ulogic;

10 signal y, z

: out std_ulogic;

1 -- concurrent

2 u1: component flipflop

port map(

clk => clk_int,

set => a,

rst => b,

Q

=> y,

Qn

=> z

);

```

#### 2.6.5 Processes

For more sophisticated logic VHDL offers a way of writing sequential statements called  $\it process.$

```

1 [label]: process ([sensitivity list])

2 -- declarations

3 begin

4 -- sequential statements

5 end process;

```

Processes have a *sensitivity list* that can be empty. When a signal in the sensitivity list changes state, the process is executed. With an empty sensitivity list, the process runs continuously. In the declaration, everything from §2.5 applies. For the sequential statements, the following applies:

- Neither selective (with) nor conditional (when) should be used. They are replaced with new sequential constructs (if and case).

- Signal assignments (with <=) change their value only at the next wait for statement or at the end of the process.

- Variables on the other hand change as soon as they are assigned (with :=).

And for good practice:

- Before any if or case default values should be assigned.

- Any signal on the RHS should be in the sensitivity list.

• Processes with empty sensitivity lists should only 2.8 Generic Parameters be used for simulations.

The sequential replacements for with and when are in the listings below.

```

1 if \langle condition \rangle then

-- sequential statements

3 elsif \langle \, condition \, \rangle then

-- sequential statements

5 else

-- sequential statements

7 end if;

1 case \langle expression \rangle is

when \langle choice \rangle =>

-- sequential statements

3

4

when \langle choice \rangle =>

5

-- sequential statements

when others =>

6

-- sequential statements

7

8 end case;

```

Processes can detect attributes of signals. Typically it is used for clocks. There are also other attributes such as s'stable(t).

```

1 process (clk)

2 begin

-- rising edge

3

4

if clk'event and clk = '1' then

5

... end if;

if rising_edge(clk) then

6

... end if;

8

9

-- falling edge

if clk'event and clk = '0' then

10

... end if;

11

if falling_edge(clk) then

12

13

... end if;

14 end process;

```

#### 2.7Pitfalls and RTL model

Coming from a programming language, a common pitfall is to write something like

```

1 -- wrong!!!

2 y <= y xor a;

```

but this will be synthesised into an oscillating circuit, that must be avoided at all costs. The correct way is to have a memory for the next state, with a logic separated into combinatorial and sequential parts.

```

1 -- combinatorial

2 y_next <= y xor a;</pre>

3 -- sequential

4 process (clk)

5 begin

if rising_edge(clk) then

y <= y_next;

end if;

9 end process;

```

This method is known as register transfer level design.

Sometimes a group of components have a very similar structure, so instead of rewriting multiple similar interfaces it is desirable to have parameters and a generic entity, for example in the case of a binary counter's range. To solve the problem using signals with conditional statements would generate unnecessary hardware, while constants cannot change the entity's port. Thus there is a syntax:

```

1 generic(

\langle param \ name \rangle : \langle type \rangle := \langle initial \ value \rangle;

[more parameters];

\langle param \ name \rangle : \langle type \rangle := \langle initial \ value \rangle

5);

```

that has affects at synthesization time.

#### 2.8.1 Generic entity and declaration

Entities are parametrized as follows.

1 entity  $\langle name \rangle$  is

10 end entity;

```

generic(( parameters ));

port (\langle pins \rangle);

4 end entity \langle name \rangle;

For example:

1 entity counter is

generic(CNT_MAX : natural := 127);

3

port(

clk, rst, ena : in std_logic;

5

-- adjust to a power of 2

6

count : out std_logic_vector(

7

(natural(ceil(

log2(real(CNT_MAX +1))) -1)

8

downto 0);

9

```

And in the architecture it is possible to access generic values in a similary way. Another example is a clock divider.

```

1 entity clockdivider is

generic(DIV_FACTOR : natural := 128);

3

port(...);

4 end entity;

6 architecture RTL of clockdivider is

signal cnt, cnt_next : natural range 0

```

#### 2.8.2 Generic mapping (Concurrent Area)

To map a generic entity into a structural design the syntax is extended accordingly with generic map().

```

1 -- definition

2 component \langle generic \ entity \rangle is

generic(( parameters ));

port (\langle pins \rangle);

5 end component;

1 [label]: component \( \text{generic component} \)

generic map(

```

### 3 State Machines

Ζ

#### 3.1 Encoding the state

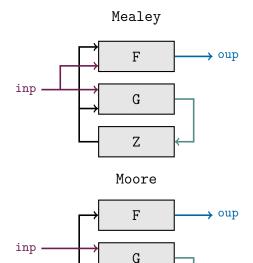

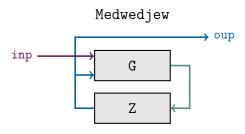

For Mealey and Moore machines it is typical to write:

The encoding of the state is left to the synthesizer or can be configured in the graphical interface of the tool. If a custom encoding is required (Medwedjew), adding the following generates a custom encoding.

```

1 attribute enum_encoding : string;

2 attribute enum_encoding of state_type:

3 type is "0001 0010 0100 ...";

```

Or an equivalent approach is to use a vector subtype and constants.

#### 3.2 Updating the state register (Z)

```

1 register_logic: process (clk, rst)

2 begin

3   -- asynchronous reset

4   if rst = '1' then

5     present_state <= st_rst;

6

7   -- clock

8   elsif rising_edge(clk) then

9     present_state <= next_state;

10   end if;

11 end process;</pre>

```

#### 3.3 Updating the state (G)

```

1 next_state_logic:

2 process (present_state, [inputs])

3 begin

-- default value

5

next_state <= state_rst;</pre>

6

7

case present_state is

8

when st_rst =>

9

-- reset state logic

10

next_state <= \langle state \rangle;</pre>

11

12

when st_a =>

13

-- logic using inputs

14

next_state \lt= \langle state \rangle;

15

16

when others => null;

17

end case;

19 end process;

```

#### 3.4 Updating the output (F)

Mealey

```

1 output_logic:

2 process (present_state, \langle inputs \rangle)

3 begin

4 -- logic with state and inputs

5 \langle output \rangle <= \langle expression \rangle;

6 end process;

Moore

1 output_logic: process (present_state)

2 begin

3 case present_state is

4 when st_rst =>

5 \langle output \rangle <= \langle value \rangle;</pre>

```

```

6

7    ...

8   end case;

9   end process;

Medwedjew

1  output_logic: \( \langle output \rangle \) <= present_state;</pre>

```

## 4 Testing

To simulate a digial circuit it is possible to write test benches using VHDL. The code in this section may no longer be synthetisable, and is usually written by a *test* designer.

#### 4.1 Simulator

VHDL simulates digital systems using delta cycles.

#### 4.2 Transport delay

To model a time delay of a signal there are two ways:

```

1 y <= transport \langle expression \rangle after \langle time \rangle;

2 y <= inertial \langle expression \rangle after \langle time \rangle;</pre>

```

When transport is used, the output changes only exactly after the specified time, the simulator simply waits. With inertial, the output is also delayed, but only if the input lasts more than the specified time. This means that for example with a time of 10 ns a pulse of 5 ns will be ignored. This is much more typical and realistic, thus when unspecified, after is interpreted as inertial ... after.

```

1 y \langle expression \rangle after \langle time \rangle;

```

#### 4.3 Generate stimuli

Simple stimuli (signals) are generated using processes. For example a clock signal done in three ways:

```

1 -- declaration

2 constant f : integer := 1000;

3 constant T : time := 1 sec/f;

4 signal clk0, clk1, clk2 : std_ulogic;

1 -- concurrent

2 clock0: process

3 begin

clk <= '1'; wait for (T/2);</pre>

clk <= '0'; wait for (T/2);</pre>

6 end process;

8 clock1: process

9 begin

clk1 <= '1';

10

11

loop

wait for (T/2);

12

clk1 <= not clk1;</pre>

13

end loop;

14

15 end process;

17 -- lazy way

18 clock2: clk2 <= not clk2 after (T/2);</pre>

```

One time stimuli can be modelled using the following expression. Note that the time is absolute.

```

1 tb_sig <= '0',

2 '1' after 20 ns,

3 '0' after 30 ns, -- 10 ns later

4 \( \langle value \rangle \) after \( \langle time \rangle \);</pre>

```

Repeating sequences can be created using processes.

```

1 sequence: process

2 begin

3    tb_sig <= '0';

4    wait for 20 ns;

5    tb_sig <= '1';

6    wait for 10 ns;

7    ...

8 end process;</pre>

```

For loops are also available, and can be synthesised if they run over a finite range.

```

1 [label]: for \langle parameter \rangle in \langle range \rangle loop

2 -- sequential statements

3 end loop [label];

```

A concrete example:

#### 4.4 Assertions

Assertions are used write tests to check that a signal is in the correct state.

```

1 [label]: assert \langle condition \rangle report \langle string \rangle

\hookrightarrow severity \langle severity \rangle;

```

The report and severity are optional but strongly advised. The severity can take one of 4 values: note, warning, error, failure. Simulations can be configured to stop in when an error of the desired severity occurs. An example:

```

1 assert (tb_y = '0') report "error at \hookrightarrow vector 11" severity error;

```

## 5 Samples / Templates

Below is a template for a simple VHDL file.

```

1 library ieee;

2 use ieee.std_logic_1164.all;

3 -- declare entities (§2.3)

4 entity (name) is

```

```

5 port([pins]);

6 end entity \langle name \rangle;

7 -- declare architectures (§2.3)

8 architecture \langle name \rangle of \langle entity \ name \rangle is

9 -- internal signals (§2.5)

-- other components (§2.6.4)

10

-- declare custom types (§3.1)

11

-- variables of custom type (§3.1)

13 begin

14 -- assignments and processes (§2.6)

15 end architecture \langle name \rangle;

And for a test bench

1 library ieee;

2 use ieee.std_logic_1164.all;

4 -- declare entities (§2.3)

5 entity \langle name \rangle_tb is

6 -- nothing here

7 end entity \langle name \rangle_tb;

9 architecture tb of \langle name \rangle_tb is

10 -- simulator settings

11 constant freq : natural := \langle frequency \rangle;

constant time : time := 1 sec / freq;

12

13

-- component of DUT

14

component \langle name \rangle is

15

port(

17

clk : in std_ulogic;

[other I/O]

18

);

19

20

end component \langle name \rangle;

21

22

signal clk_tb : std_ulogic;

23

-- more signals for inputs and outputs

24 begin

25

dut: component (name)

26

27

port map(

clk => clk_tb;

28

\langle other I/O \rangle);

29

30

31

clk_generator: process

-- generate clock (§4.3)

32

clk_tb <= '1'; wait for (T/2);

33

clk_tb <= '0'; wait for (T/2);

34

end process;

35

36

37

stimuli: process

38

begin

-- generate stimuli (§4.3)

39

40

-- for loops, after, etc.

41

end;

42

response: process

43

44

-- constants for expected outputs

begin

45

wait for 0.9 * T;

47

-- assertions (§4.4)

wait for T;

48

49

end process;

50

51 end architecture tb;

```