# DigDes: Digital Design

## $Naoki\ Pross-{\tt naoki.pross@ost.ch}$

## Spring Semester 2021

## Contents

| 1        | Lice                                       | ense    |                                      | 1 |  |

|----------|--------------------------------------------|---------|--------------------------------------|---|--|

| <b>2</b> | VHSIC Hardware Description Language (VHDL) |         |                                      |   |  |

|          | 2.1                                        | Basic   | syntax and identifiers               | 2 |  |

|          | 2.2                                        | Entitie | es and Architectures                 | 2 |  |

|          | 2.3                                        | Electr  | ic types and Libraries               | 2 |  |

|          | 2.4                                        | Declar  | rations                              | 2 |  |

|          | 2.5                                        |         | rrent Area                           |   |  |

|          |                                            | 2.5.1   | Signal assignment and simple gates   | 3 |  |

|          |                                            |         | Aggregates                           |   |  |

|          |                                            | 2.5.3   | Seiective and conditional assignment | 3 |  |

|          |                                            | 2.5.4   | Processes                            | 3 |  |

## 1 License

This work is licensed under a Creative Commons "Attribution-NonCommercial-ShareAlike 4.0 International" license.

## 2 VHSIC Hardware Descrip- 2.3 Electric types and Libraries tion Language (VHDL)

## Basic syntax and identifiers

In VHDL an identifier is a case insensitive string composed of A-Z a-z 0-9 \_ that

- is not a keyword,

- does not start with a number or \_,

- does not have two or more \_ in a row.

Expressions are terminated by a semicolon; Two dashes in a row cause the rest of the line to be interpreted as a comment.

```

1 expression; -- comment

```

### **Entities and Architectures**

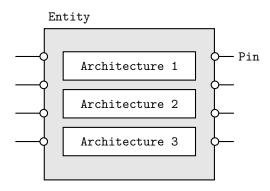

In VHDL the concept of entity describes a black box of which only inputs and outputs are known. The internals of an entity are described through an architecture. There can be multiple architectures for a single entity.

Entities are declared with port() that may contain a list of pins. Pins have a mode that can be in input (only LHS), out output (only RHS), inout bidirectional or buffer that can stay both on LHS and RHS. The usage of the latter is discourareged in favour of an internal signal.

```

1 entity \langle name \rangle is

port(

\langle pin \rangle : \langle mode \rangle \langle type \rangle;

4

);

5 end \langle name \rangle;

```

Architectures are normally named after the design model, example are behavioral, structural, selective, etc.

```

1 architecture \langle \, name \, \rangle of \langle \, entity \, \rangle is

-- declare used variables, signals

\hookrightarrow and component types

3 begin

-- concurrent area

5 end [name];

```

VHDL provides some types such as

- boolean true or false,

- bit 0 or 1.

- bit vector one dimensional array of bits,

- integer 32-bit binary representation of a value.

From external libraries other types are available:

- std\_logic advanced logic with 9 states,

- std\_ulogic

The above are from the ieee.std logic 1164 library, and can take the values described in the following table.

| Value | Meaning        | Usage                                               |

|-------|----------------|-----------------------------------------------------|

| U     | Uninitialized  | In the simulator                                    |

| Х     | Undefined      | Simulator sees a bus conflict                       |

| 0     | Force to 0     | Low state of outputs                                |

| 1     | Force to 1     | High state of outputs                               |

| Z     | High Impedance | Three state ports                                   |

| W     | Weak Unknown   | Simulator sees weak a bus conflict                  |

| L     | Weak Low       | Open source outputs<br>with pull-down re-<br>sistor |

| Н     | Weak High      | Open drain output with pull-up resistor             |

|       | Don't care     | Allow minimization                                  |

### Declarations

Before a begin - end block, there is usually a list of declarations. A self evident examples are *constants*.

```

1 constant \langle name \rangle : \langle type \rangle := \langle value \rangle;

```

Next, signals and variables. Signals is are wires, they can only be connected and do not have an initial state. Variables can be assigned like in software, but can cause the synthesization of an unwanted D-Latch.

```

1 signal \langle name \rangle, \lceil name, ... \rceil : \langle type \rangle;

3 variable \langle name \rangle, [name], [...] : \langle type \rangle;

4 variable \langle name \rangle : \langle type \rangle := \langle expression \rangle;

```

For the hierarchical designs, when external entities are used, they must be declared as components. The port() expression must match the entity declaration.

```

1 component \langle entity \ name \rangle is

port(

[list of pins]

);

5 end component;

```

It is possible to create custom types, usually to 2.5.3 Selective and conditional assignment create state machines.

```

1 type \langle name \rangle is (\langle identifier \rangle, \langle identifier \rangle,

\hookrightarrow ...);

```

### 2.5 Concurrent Area

## Architecture у clk Logic Process Gate a Component b Entity

In the architecture between begin and end, the expressions are not read sequentially, everything happens at the same time. Statements inside the concurrent area optionally have a label.

```

1 [label]: \( \concurrent \statement \);

```

In the concurrent area signals, components and processes can be used to create a logic.

## 2.5.1 Signal assignment and simple gates

Signals are assigned using <=.

```

1 [label]: \langle signal \rangle \leftarrow \langle expression \rangle;

```

Simple logic functions such as not, and, or, xor, etc. can be used.

```

1 y \le (a \text{ and } s) \text{ or } (b \text{ and } not(s));

```

## 2.5.2 Aggregates

For vector types it is possible to create a value out of multiple signals.

```

1 \ \langle vector \rangle \le

\langle index \rangle = > \langle source \ or \ value \rangle,

\langle index \rangle => \langle source \ or \ value \rangle,

[others] => \(\langle source \) or value \(\rangle \)

5);

1 -- declaration

2 signal data : bit_vector(6 downto 0);

3 signal a, b : bit;

4 -- concurrent

5 data = (1 => a, 0 => b, others => '0')

```

Higher level conditions can be written in two ways.

```

1 -- using when

2 [label]: y <= \langle source \rangle when \langle condition \rangle else

\langle source \rangle when \langle condition \rangle else

⟨source⟩ when ⟨condition⟩;

-- using with

7 [label]: with \langle signal \rangle select \langle dest \rangle <=

\langle source \rangle when \langle value \rangle,

\langle source \rangle when \langle value \rangle,

\langle source \rangle when others;

```

### 2.5.4 Processes

For more sophisticated logic, VHDL offers a way of writing sequential statements called *processes*.

```

1 [label]: process ([sensitivity list])

2 -- declarations

3 begin

-- sequential statements

5 end process;

```

Processes have a sensitivity list that could also be empty. When a signal in the sensitivity list changes state, the process is executed. In the case of an empty sensitivity list, the process runs continuously. In the declaration, everything from §2.4 applies. For the sequential statements, the following applies:

- Neither selective (with) nor conditional (when  $\rightarrow$  ) should be used, as there because there are new sequential constructs (if and case).

- Signal assignments (with <=) change their value</li> only at the end of the process.

- Variables on the other hand change as soon as they are assigned (with :=).

And for good practice:

- Before any if or case default values should be assigned.

- Any signal on the RHS should be in the sensitivity list.

- Processes with empty sensitivity lists should only be used for simulations.

The sequential replacements for with and when are in the listings below.

```

1 if \langle condition \rangle then

-- sequential statements

3 elsif \langle \, condition \, \rangle then

-- sequential statements

5 else

-- sequential statements

7 end if;

```

```

1 case \( \left( expression \right) \) is

2    when \( \left( choice \right) = \right)

3          -- sequential statements

4    when \( \left( choice \right) = \right)

5          -- sequential statements

6    when others = \right>

7          -- sequential statements

8 end case;

```

Processes can detect events of signals. Typically this is used for clocks.

```

1 process (clk)

2 begin

3 -- rising edge

4 if clk'event and clk = '1' then

... end if;

6 if rising_edge(clk) then

... end if;

7

8

9

-- falling edge

if clk'event and clk = '0' then

10

11

... end if;

12 if falling_edge(clk) then

13 ... end if;

14 end process;

```